Nios II

出典: くみこみックス

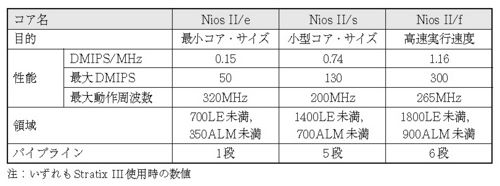

広範囲の組み込みアプリケーション向けに設計された汎用RISCアーキテクチャを特徴とする,Altera社が提供するソフト・マクロのCPUコアです(図1).Nios IIは,SOPC Builderを使用してFPGA内のシステムに追加します.目的に応じて3種類のコアが用意されています(表8).Nios IIは,レジスタ・ファイル,演算論理ユニット,例外・割り込みコントローラ,命令/データ・バス,命令/データ・キャッシュ,およびJTAGデバッグ・モジュールを備えています.

また,Nios IIの特徴として,カスタム命令を追加する機能が挙げられます.これは,ソフトウェアの複雑な動作シーケンスを,ハードウェアで実装された一つの命令にまとめ,ソフトウェアよりも高速に実行できるようにする機能です(図2).Nios IIには,これらの機能に加えて,メモリ管理ユニット(MMU),メモリ保護ユニット(MPU),ハードウェア・アクセラレータなどの機能も用意されています.

【出典】(株)アルティマ 技術統括部 一同,下馬場 朋禄,山際 伸一,横溝 憲治;システム開発者のためのFPGA用語集,Design Wave Magazine 2008年12月号 別冊付録,CQ出版社,2008年12月.