シリコン・ウェハ

出典: くみこみックス

版間での差分

| 1 行 | 1 行 | ||

シリコン・ウェハ 【Silicon Wafer】 | シリコン・ウェハ 【Silicon Wafer】 | ||

| - | 円柱状のケイ素の単結晶を1mm程度に薄く切り,フォトマスクで光学的にn/ | + | 円柱状のケイ素の単結晶を1mm程度に薄く切り,フォトマスクで光学的にn/pチャネルのトランジスタ素子と配線をエッチングすることにより,複数の[[ダイ]](半導体チップ)を形成した板のことをいいます('''写真'''). |

| - | + | ||

| - | + | ||

| - | + | ||

| - | + | ||

<br> | <br> | ||

<br> | <br> | ||

| 14 行 | 10 行 | ||

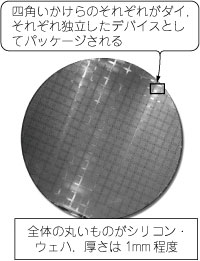

'''写真 シリコン・ウェハの外観''' | '''写真 シリコン・ウェハの外観''' | ||

</center> | </center> | ||

| + | |||

| + | <br> | ||

| + | <br> | ||

| + | 【出典】(株)アルティマ 技術統括部 一同,下馬場 朋禄,山際 伸一,横溝 憲治;システム開発者のためのFPGA用語集,Design Wave Magazine 2008年12月号 別冊付録,CQ出版社,2008年12月. | ||

| + | <!-- 【著作権者】○○ ○○氏 --> | ||

| + | <br> | ||

| + | <br> | ||

== 関連項目 == | == 関連項目 == | ||

最新版

シリコン・ウェハ 【Silicon Wafer】

円柱状のケイ素の単結晶を1mm程度に薄く切り,フォトマスクで光学的にn/pチャネルのトランジスタ素子と配線をエッチングすることにより,複数のダイ(半導体チップ)を形成した板のことをいいます(写真).

【出典】(株)アルティマ 技術統括部 一同,下馬場 朋禄,山際 伸一,横溝 憲治;システム開発者のためのFPGA用語集,Design Wave Magazine 2008年12月号 別冊付録,CQ出版社,2008年12月.