Stratix

出典: くみこみックス

版間での差分

| 7 行 | 7 行 | ||

<br> | <br> | ||

<br> | <br> | ||

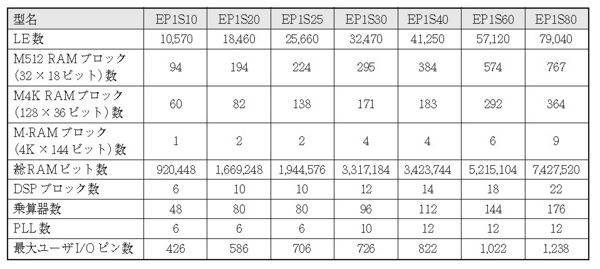

| + | '''表1 Stratixファミリの概要'''<br> | ||

[[画像:fpga_t10.jpg|600px]]<br> | [[画像:fpga_t10.jpg|600px]]<br> | ||

<br> | <br> | ||

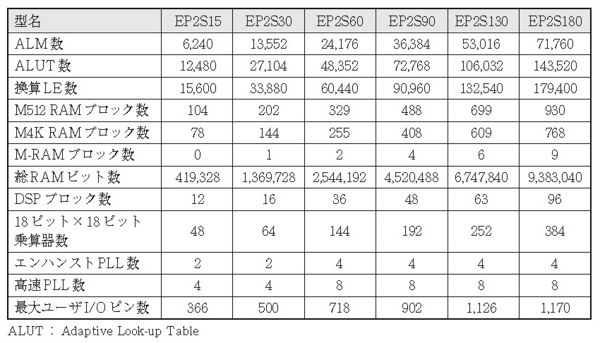

| + | '''表2 Stratix IIファミリの概要'''<br> | ||

[[画像:fpga_t11.jpg|600px]]<br> | [[画像:fpga_t11.jpg|600px]]<br> | ||

<br> | <br> | ||

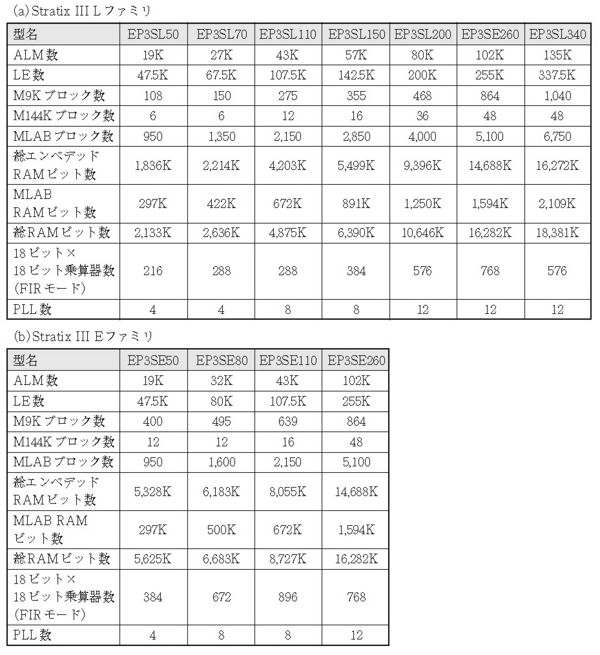

| + | '''表3 Stratix IIIファミリの概要'''<br> | ||

[[画像:fpga_t12.jpg|600px]]<br> | [[画像:fpga_t12.jpg|600px]]<br> | ||

<br> | <br> | ||

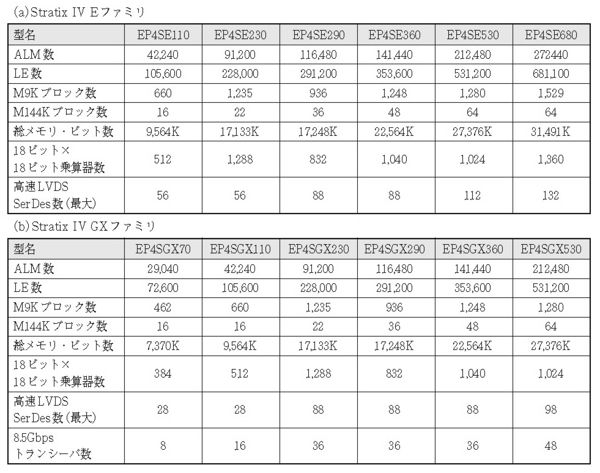

| + | '''表4 Stratix IVファミリの概要'''<br> | ||

[[画像:fpga_t13.jpg|600px]]<br> | [[画像:fpga_t13.jpg|600px]]<br> | ||

[[Category:組み込み技術全般]] [[Category:FPGA]] | [[Category:組み込み技術全般]] [[Category:FPGA]] | ||

2009年2月3日 (火) 06:40の版

StratixはAltera社のハイエンドFPGAシリーズで,第4世代のStratix IVシリーズが2009年から量産出荷されます.各世代の製造プロセスは,Stratixが130nm,Stratix IIが90nm,Stratix IIIが65nm,そして最新のStratix IVが40nmです(表10〜表13).Stratix IVは,最大681,100LE相当のロジック,30Mビットのエンベデッド・メモリ,1,360個のDSPブロック,12個のPLLなどを搭載しており,8.5Gbpsのトランシーバを内蔵したStratix IV GXもあります.

【出典】(株)アルティマ 技術統括部 一同,下馬場 朋禄,山際 伸一,横溝 憲治;システム開発者のためのFPGA用語集,Design Wave Magazine 2008年12月号 別冊付録,CQ出版社,2008年12月.

表1 Stratixファミリの概要