プリエンファシス

出典: くみこみックス

版間での差分

| 11 行 | 11 行 | ||

<center> | <center> | ||

[[画像:fpga_f43a.jpg]]<br> | [[画像:fpga_f43a.jpg]]<br> | ||

| - | |||

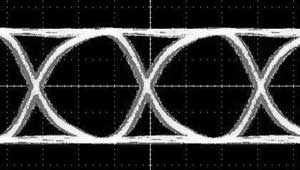

'''図 プリエンファシス適用前'''<br> | '''図 プリエンファシス適用前'''<br> | ||

<br> | <br> | ||

[[画像:fpga_f43b.jpg]]<br> | [[画像:fpga_f43b.jpg]]<br> | ||

| - | |||

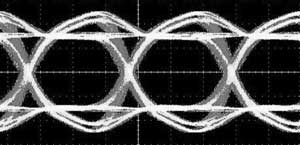

'''図 プリエンファシス適用後''' | '''図 プリエンファシス適用後''' | ||

</center> | </center> | ||

[[Category:組み込み技術全般|フリエンファシス]] [[Category:FPGA|フリエンファシス]] | [[Category:組み込み技術全般|フリエンファシス]] [[Category:FPGA|フリエンファシス]] | ||

2009年2月2日 (月) 02:05の版

プリエンファシス 【Pre-emphasis】

伝送媒体による高周波帯域の損失を補償するためにデータ信号を増幅する方法です(図).高周波の信号は伝送される途中で品質が落ちるため,プリエンファシスが考え出されました.例えばAltera社のFPGAの場合,四つの異なる設定が用意されており,さまざまな配線パターン長や伝送線路特性,電源特性を調整および補償することができます.

【出典】(株)アルティマ 技術統括部 一同,下馬場 朋禄,山際 伸一,横溝 憲治;システム開発者のためのFPGA用語集,Design Wave Magazine 2008年12月号 別冊付録,CQ出版社,2008年12月.